# Connect your real (sub)system to your

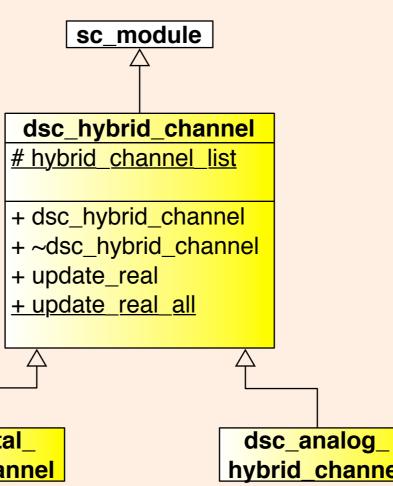

update\_real functionality.

# Hardware-in-the-loop for Hardware/Software Co-design of Real-time Embedded Systems SIEMENS Doğan Fennibay<sup>1, 2</sup>Arda Yurdakul<sup>2</sup>, Alper Şen<sup>2</sup>

neering, Boğazici University, İstanbul dogan.fennibay@siemens.com, yurdakul@boun.edu.tr, alper.sen@boun.edu.tr

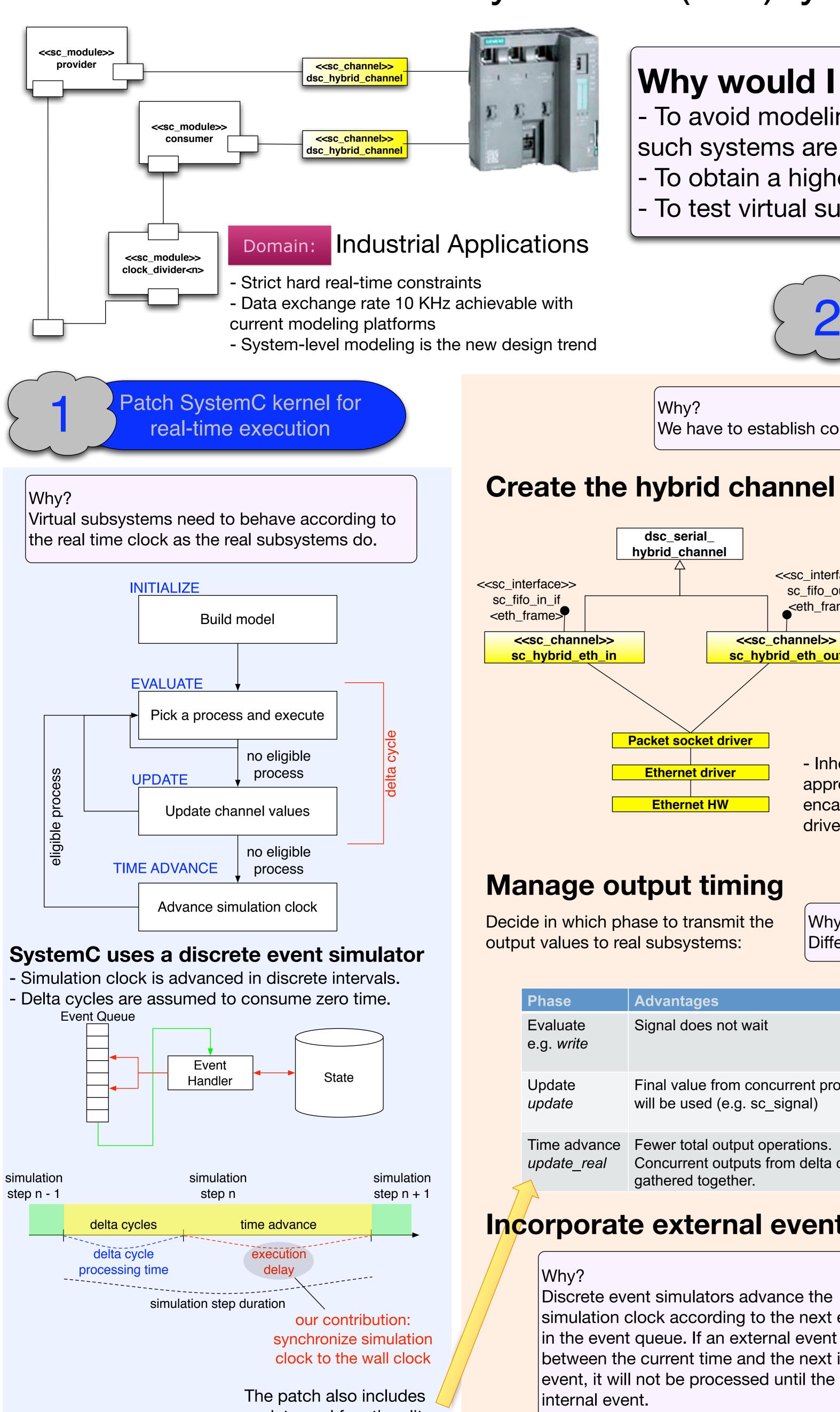

# Why would I want to do that?

- To avoid modeling complex systems when physical implementations of such systems are available.

- To obtain a higher modeling accuracy with less modeling effort.

- To test virtual subsystems with a real testbed.

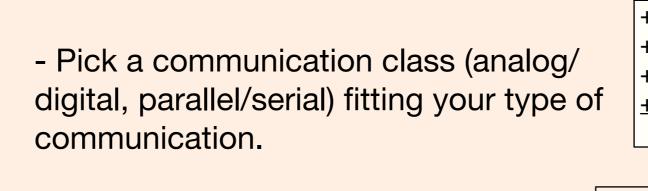

- Inherit your SystemC channel from the hybrid\_channel appropriate hybrid channel class and encapsulate the integration to the I/O driver inside.

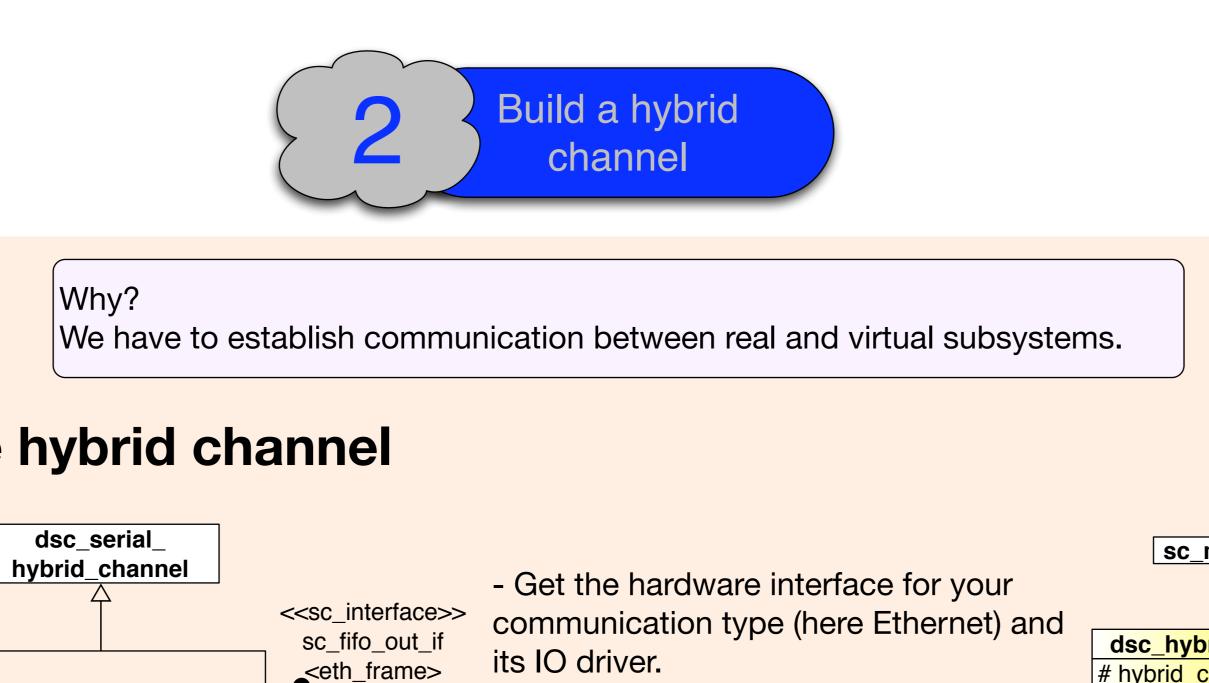

Manage output timing

Ethernet driver

Ethernet HW

Why? Different types of communication need different timing of output operations.

| Advantages                                                                                   | Disadvantages                                                                                                             | Exam    |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------|

| Signal does not wait                                                                         | Signal value has to remain the same in later<br>delta cycles. (e.g. sc_fifo)<br>High number of output operations.         | An Eth  |

| Final value from concurrent processes will be used (e.g. sc_signal)                          | Processing time of update phase increases.<br>Concurrent outputs w.r.t. the simulation clock<br>distributed in real-time. | A digit |

| Fewer total output operations.<br>Concurrent outputs from delta cycles<br>gathered together. | Glitches occurring at the end of delta cycles not transmitted to the real subsystems.                                     | APW     |

## Incorporate external events (inputs)

<<sc\_channel>>

sc\_hybrid\_eth\_out

Discrete event simulators advance the simulation clock according to the next element in the event queue. If an external event occurs between the current time and the next internal event, it will not be processed until the next

- Use an asynchronous OS thread to get the external event which sets a fast-to-check flag for SystemC. (optional) - Specify a polling rate.

dsc\_digital\_

dsc\_serial\_

hybrid channel

- Poll the external event at the specified rate from a dedicated SystemC thread and set a SystemC event on detection.

- Rest of the model can use that event.

hernet channel

ital I/O channel

/M motor driver

### Why?

Non-determinism in OS reduces predictability of virtual subsystems and therefore decreases accuracy of the whole model.

## **RTOS vs. GPOS**

- GPOS: More facilities, I/O interfaces - RTOS: Deterministic behavior. **Proposed solution: GPOS with real**time improvements (Linux with RT PREEMPT)

### Improvements in OS

- Patch the Linux kernel with RT PREEMPT.

- Interrupt handlers moved to thread context

- Spinlocks made preemptible

- Priority inheritance implemented

- for semaphores and spinlocks - Linux timers replaced with high resolution counterparts

- Turn off power management

- Disable swap memory

### **Application settings**

- Set application threads to real-time scheduling and set priorities. - Extend thread stacks at initialization to avoid page faults during execution.

### Latency hunting

- Eliminate further sources of latency (corrupt driver, hardware causing unnecessary interrupts etc.) - Use ftrace facility of Linux for diagnosis.

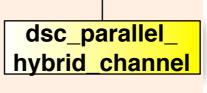

| 1800 µs - |           |

|-----------|-----------|

| 1600 µs - |           |

| 1400 µs - |           |

| 1200 µs - |           |

| 1000 µs - |           |

| 800 µs  ⁻ |           |

| 600 µs -  |           |

| 400 µs -  |           |

| 200 µs -  |           |

| 0 µs -    |           |

|           | 64 bytes, |

|           | μs        |

|           |           |

|           |           |

| 45,00% - |    |

|----------|----|

| 43,0070  |    |

| 40,00% - |    |

|          |    |

| 35,00% - |    |

| 20.00%   |    |

| 30,00% - |    |

| 25,00% - |    |

| -        |    |

| 20,00% - |    |

| 45.000/  |    |

| 15,00% - |    |

| 10,00% - |    |

| -,       |    |

| 5,00% -  |    |

|          |    |

| 0,00% -  |    |

| 0,0      | 01 |

|          |    |

simple model. jitter is the problem.

| %25,0         |    |

|---------------|----|

| %20,0 -       |    |

| %15,0 -       |    |

| ****          |    |

| %10,0 -       |    |

| %5,0 -        |    |

| %0,0 -<br>0,0 | 01 |

|               |    |

Square wave generation: maximum jitter / desired period - Frequency sustained up to 10 KHz, unstable at 100 KHz - CPU load has minimal effect, OS scheduler working fine - Measurements coincide with internal measurements above, main factor is the simulation performance rather than the I/O performance.

\_\_\_\_\_

**Desired frequency [KHz]**

– – w/o CPU load with CPU load